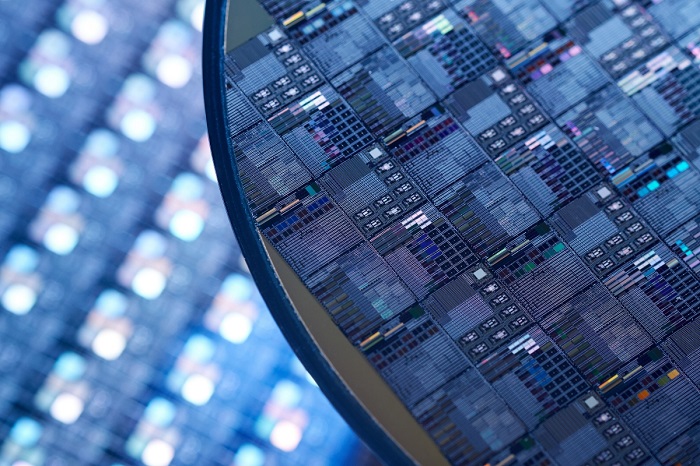

بنا بهگفتهی منابع وبسایت حوزهی فناوری، Digi Times در صنعت تولید تراشه، شرکت صنایع نیمههادی تایوان (TSMC) تولید انبوه تراشههای خود با لیتوگرافیِ ۵ نانومتری را از ماه مارس سال ۲۰۲۰ میلادی آغاز میکند. زمانیکه شرکتها از از PDK یا همان کیت طراحیِ فرایندی ۵ نانومتری استفاده کنند، میتوانند طراحیِهایشان را بهسادگی در محصولات آینده مورد استفاده قرار دهند.

دو سال پس از آنکه تراشههای با لیتوگرافیِ ۷ نانومتری به تولید انبوه رسیدند، تراشههای ۵ نانومتری، تلاشی برای ادامهی مسیر تولید تراشه در راستای قانون مور و اثبات آن هستند. قانون مور، قاعدهای سرانگشتی است که بیان میکند تعداد ترانزیستورهای روی یک تراشه با مساحت ثابت، هر دو سال بهطور تقریبی دو برابر میشوند. مدیر بخش بازاریابی TSMC اخیرا در پستی که در وبلاگ خود منتشر کرده بود، اعلام کرد قانون مور هنوز نمرده و به قوت خود باقی است.

ترانزیستورهای FinFET موجود در تراشههای ۵ نانومتری تولید شده با لیتوگرافیِ Extreme Ultra-Violet یا بهاختصار EUV بهمعنای اشعهی ماوراء بنفش حد بالا، در مقایسه با تراشههای ۷ نانومتری، احتمالا بهبودهای عملکردیِ بسیاری در زمینهی سرعت، قدرت و تراکم خواهند داشت. پیشبینی میشود در حالی که تراکم بیش از ۸۰% بهبود مییابد، سرعت عملکرد تا حدود ۱۵% افزایش یابد که پیشرفت چشمگیر و قابل توجهی در توسعهی تراشهها محسوب میشود. همچنین این تراشهها با کاهش توان مصرفی همراه هستند که باعث کاهش مصرف برق تا حدود ۳۰% میشود. این در حالی است که تراشههای جدید علاوه بر سرعت بیشتر، از تراکم بیشتری نیز بهره میبرند که امکان الحاق گرههای بیشتر به تراشه را میدهد.

.: Weblog Themes By Pichak :.